ustry

e and

e and

er wire

ttors

and cable

uots

filips

# M

#### Design Ideas

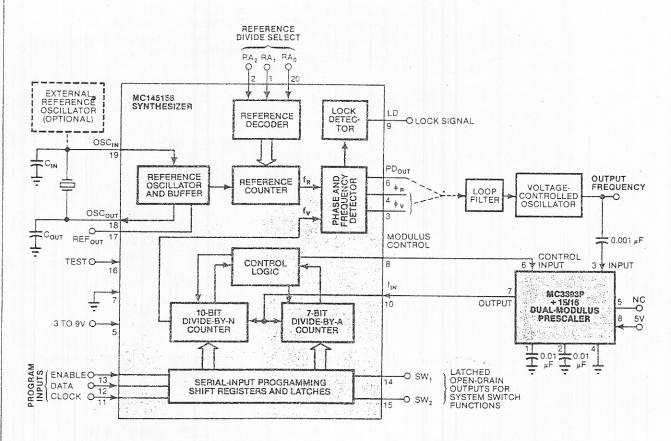

### Versatile synthesizer controls 140 MHz

John Hatchett and William Morgan Motorola Inc, Phoenix, AZ

Dual-module prescaling is a standard technique for achieving high-performance, high-frequency phase-locked-loop frequency-synthesizer designs (references). Unfortunately, these designs often require

eight to 12 ICs to provide true versatility. However, the 2-IC scheme outlined in the figure can directly control a synthesizer to 140 MHz. And by employing a higher frequency chip (such as the MC12009, 11 or 13) and a range-extending prescaler, you can push the concept to 500 MHz.

The MC3393P functions as a dual-modulus prescaler when the MC145156 frequency synthesizer's Modulus Control signal selects its divisor (15 or 16).

| REFERENCE DIVIDE<br>SELECT |                 |     | TOTAL REFERENCE<br>DIVIDE VALUE |

|----------------------------|-----------------|-----|---------------------------------|

| RA <sub>2</sub>            | RA <sub>1</sub> | RAo |                                 |

| 0                          | 0               | 0   | 8                               |

| 0                          | 0               | 1.  | 64                              |

| 0                          | 1               | 0   | 128                             |

| 0                          | 1               | 1 , | 256                             |

| 1                          | 0               | 0   | 640                             |

| 1                          | 0               | 1   | 1000                            |

| 1                          | 1               | 0   | 1024                            |

| 1                          | 1               | 1   | 2048                            |

NOTE: \*CHOICE OF 3-STATE (PD<sub>OUT</sub>) OR DOUBLE-ENDED ( $\phi$  <sub>R</sub>, $\dot{\phi}$  <sub>V</sub>) ERROR SIGNALS

Controllable frequency synthesis results when you combine a 2-divider phase-locked-loop IC with a dual-modulus prescaler. Loop divisor ratios span 210 to 15,374, and output frequency can reach 140 MHz typ.

OVER

#### Design Ideas

Because the prescaler's divisor gets controlled in this specific, timed-format method, the frequency synthesizer's relatively low-speed  $\div N$  and  $\div A$  counters take on the prescaler's high-frequency attributes.

Achieve an overall integer divide ratio ( $N_{TOTAL}$ ) by programming the counters with the factors 15N+A for  $X \le A$ , this programming yields an  $N_{TOTAL}$  spanning 210 to 15,374. Normally, you program A with values of 0 through 14 for a given N, increment N by 1 and repeat A's values. If you use the indicated 156-type synthesizer IC, counters N and A receive their data via a clocked, serial data stream through the Clock, Data and Enable inputs. Substituting an MC145152 in this socket permits parallel input programming; alternatively, you can employ an MC145146 in 4-bit-data-bus applications.

#### References

Nichols, J, and Shinn, C, "Pulse Swallowing," *EDN*, October 1, 1970, pgs 39-42.

"The Technique of Direct Programming by Using a Two-Modulus Prescaler," Application Note AN-827, Motorola Inc, Semiconductor Group, 1981.

To Vote For This Design, Circle No 469

#### **NEXT TIME**

EDN's November 25 issue will feature a Special Report on power semiconductors, along with a variety of useful articles on other topics:

- How to build an advanced DTMF receiver using only two ICs

- How to set up measurement instrumentation to check your designs' compliance with FCC EMI regulations

- How to use CMOS DACs in a variety of control applications

... and much more. Also look for Part 3 of our Designer's Guide to thick-film hybrid circuits, plus Technology Updates on signature-analysis instruments and independent testing labs, plus our regular Design Ideas and  $\mu C$  Design Techniques departments. You can't afford to miss this issue!

EDN: Everything Designers Need

## Design Entry Blank

\$40 Cash Award for all entries selected by editors. An additional \$75 Cash Award for winning design each issue, determined by vote of readers. Additional \$1000 Cash Award for annual Grand Prize Design, selected among biweekly winners by vote of editors.

To: Design Ideas Editor

EDN

Cahners Publishing Co

221 Columbus Ave, Boston. MA 02116

I hereby submit my entry for

EDN's Design Ideas program.

| Name               | * |       |  |

|--------------------|---|-------|--|

| Title              |   | Phone |  |

| Company            |   |       |  |

| Division (if any)  |   |       |  |

| Street             |   |       |  |

| City               |   |       |  |

| Design Title       |   |       |  |

| Home Address       |   |       |  |

|                    |   |       |  |

|                    |   |       |  |

|                    |   |       |  |

|                    |   |       |  |

| Social Security No |   |       |  |

Entry blank must accompany all entries. Design entered must be submitted exclusively to EDN, must be original with author(s), must not have been previously published (limited-distribution house organs excepted), and must have been constructed and tested.

Exclusive publishing rights remain with Cahners Publishing Co unless entry is returned to author or editor gives written permission for publication elsewhere.

In submitting my entry, I agree to abide by the rules of the Design Ideas Program.

| Signed |  |  |

|--------|--|--|

| Date   |  |  |

Your vote determines this issue's winner. All designs published win \$40 cash. All issue winners receive an additional \$75 and become eligible for the annual \$1000 Grand Prize.

**Vote now**, by circling the appropriate number on the reader inquiry card.

**Submit your own design,** too. Mail entries to Design Ideas Editor, EDN, 221 Columbus Ave, Boston, MA 02116.

Mo Reference To 145150 Being Comos